1. 페이징 메모리 기법 - (32비트 CPU, 페이지의 크기 : 8KB, 1GB 물리 메모리)

논리 주소의 비트

페이지 번호 32- 13 = 19비트, offset번호 13비트( 2^3(=8) * 2^10(=1KB))

페이지와 프레임 크기

페이지크기, 프레임 크기 모두 8KB이다.

물리 메모리에 프레임

1GB / 8KB = 2^30 / 2^13 = 2^17 개 프레임이 존재한다. 약 128,000개이다.

사용자 주소 공간의 크기가 2GB일 때, 응용프로그램의 크기

2GB이다. 32비트 CPU에서 4GB의 메모리에서 커널공간을 제외한 사용자가 사용 가능한 메모리 공간이 2GB이기 때문이다.

페이지 테이블의 한 항목 크기가 4바이트일때, 페이지 테이블의 크기

4GB의 메모리는 최대 페이지 크기는 페이지 크기로 나눈값이다.

(2^2 * 2^30) / (2^3 * 2^10) = 2^19개이다.

페이지 테이블의 한 항목이 4바이트이므로 페이지테이블 크기는

2^19 * 2^2 = 2^21

2 MB이다.

100개의 프로세스가 실행될때 전체 페이 지 테이블의 크기

100 * 페이지테이블의 크기 = 200MB이다.

프로세스가 현재 60000바이트를 사용할때, 페이지의 개수와, 물리 프레임 개수

실제 운영체제들은 코드, 데이터, 힙 등을 쉽게 관리하기 위해 새 페이지에서 시작하도록 배치하지만, 이를 배재하면

60000 / 8192(= 8KB) = 7.324...

총 8개의 물리 페이지가 필요하다.

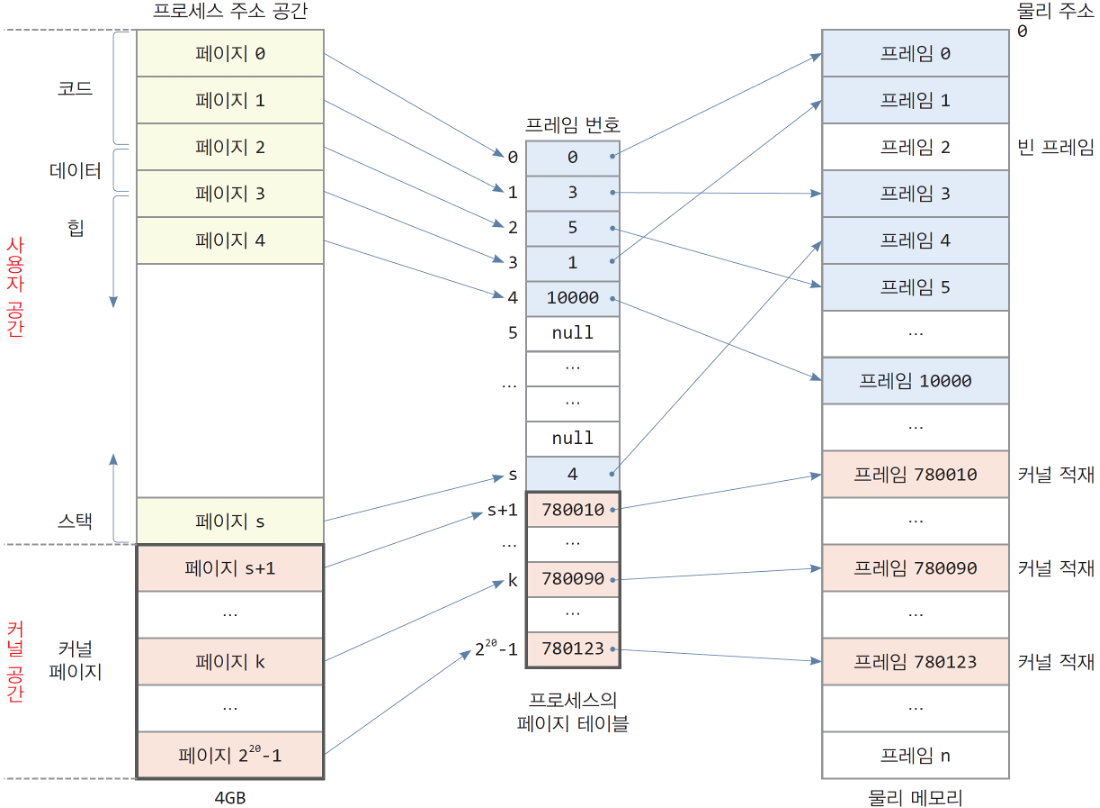

커널만을 위한 페이지 테이블?

별도로 있지 않다. 커널코드 또한, 논리 주소로 되어있고 시스템 호출을 통해 커널 코드가 실행될때 현재 프로세스의 페이지 테이블을 이용항여 물리 주소로 반환된다.

페이지 테이블은 프로세스마다 있는가?

페이지 테이블은 프로세스마다 있다.

모든 프로세스가 모든 물리 메모리 최대 주소까지 사용할 수 있게 프로그램되기 때문에 멀티 프로세스 운영체제에서 시스템 전체에 한개만 둘 수 없다.

페이지 테이블의 위치

물리메모리 커널공간에 PCB와 함께 있다. 페이지 테이블의 크기는 MB단위로 크기 때문에 메모리에 저장한다. 다만, 참조의 지역성 덕분에 일부 페이지 테이블을 TLB에 복사해놓는다.

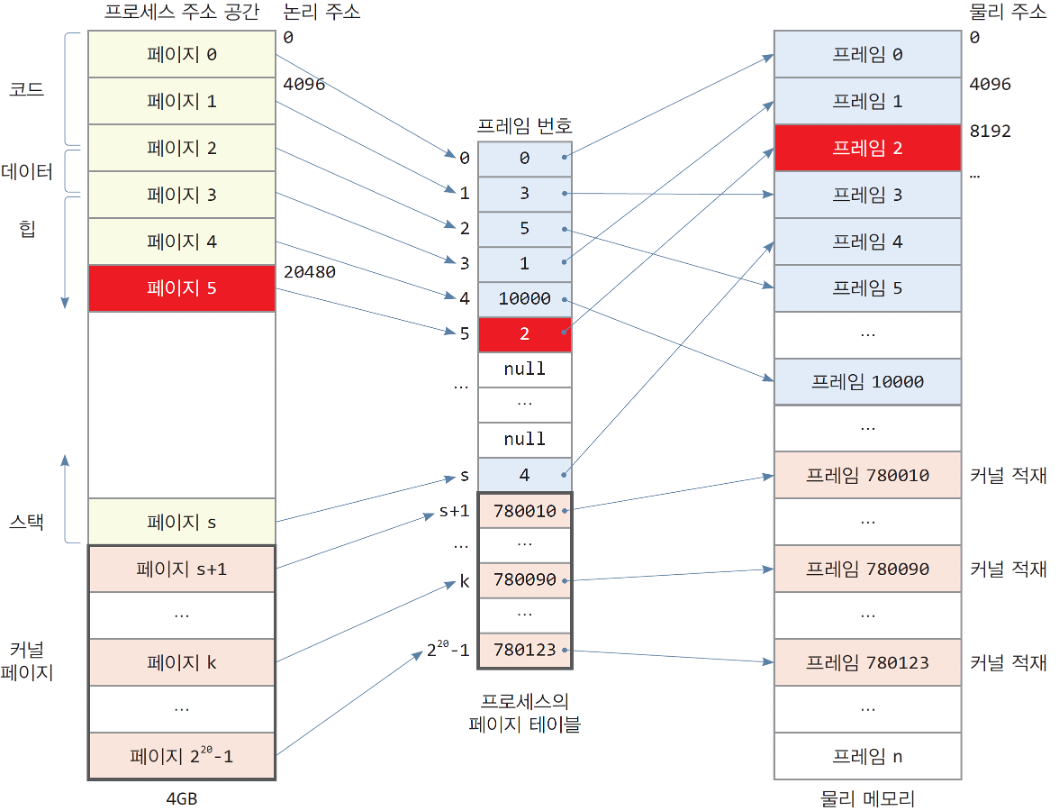

3. 그림과 같은 이 상황에서 다음 코드가 순서대로 실행될 때 각 경우에 대해 어떻게 변해 가는 과정

char *a = (char*)malloc(1000);

char *b = (char*)malloc(2000);

char *c = (char*)malloc(2000);

char *d = (char*)malloc(2000);a)

1000 바이트 할당 요청

논리 페이지 5에 남은 공간에 1000 바이트 할당

malloc은 주소 20680(20480 + 200)을 리턴

b)

2000 바이트 할당 요청

논리 페이지 5에 남은 공간에 2000 바이트 할당

malloc은 주소 21680(20680 + 1000)을 리턴

c)

2000 바이트 할당 요청

논리 페이지 5에 남은 공간에 896 바이트 할당

논리 페이지 6 할당, 물리 프레임 6 할당

페이지 테이블 항목 6에 물리프레임 번호 6 기록

malloc은 주소 23480(21680 + 2000)을 리턴

d)

2000 바이트 할당 요청

논리 페이지 6에 남은 공간에 2000 바이트 할당

malloc은 주소 25480(23680 + 2000)을 리턴

(그림)

4. TLB

TLB의 의치

CPU패키지 안에 캐시 메모리에 존재한다.

TLB의 특별히 다른점

페이지 번호로 전체 캐시를 동시에 고속 검색, 프레임 번호 출력할 수 있다.

content-addressable memory, associative memory라고 불린다.

TLB 내용은 페이지 테이블의 일부분?

그렇다. 페이지 테이블 일부분을 복사해오기 때문이다.

TLB를 사용하는 목적

TLB를 사용해 heat하면, 2번의 메모리 접근 없이 1번만에 메모리에 접근 할 수 있어 메모리 접근에 실행 속도가 빨라진다.

TLB의 유효성

TLB는 참조의 지역성으로 인해 효과적인 전략이다.

TLB의 크기

고가이기 때문에 작은 크기를 가진다. 64~1024개의 항목 정도 저장한다.

페이지의 크기가 4KB이고 TLB 항목이 1024개일때, TLB reach

(TLB 항목 수 * 페이지 크기)를 TLB reach라고 하며 4MB이다.

TLB가 채워졌을 때, 미스없이 작동하는 메모리 액세스 범위를 뜻한다.

TLB의 가격이 비싼 이유

모든 항목들을 동시에 비교하는 하드웨어 회로를 필요로 하기 때문에 가격이 비싸다.

5. 연속 메모리 참조

int n[3000];

int sum = 0;

for(i=0; i<3000; i++)

sum += n[i]; // 여기서 n[i] 액세스

- 32비트 CPU에서 실행되고, 페이지의 크기는 4KB이다.

- int는 4바이트이다.

- 배열 n의 논리 주소는 0x2000부터 시작한다.

- 배열 n이 적재되는 물리 주소는 학생이 마음대로 설정하라.

- 페이지 테이블은 0xA000에서 부터 시작된다.

TLB가 없는 경우 물리 메모리 엑세스 횟수

값을 알기 위해 물리주소에 있는 페이지 테이블 한번, 테이블 테이블을 참조해서 만든 물리주소 한번 총 두번씩 엑세스되어

6000번 물리 메모리에 엑세스한다.

항목이 4개인 TLB가 있는 경우 물리 메모리 액세스 횟수

첫째줄에서 3000*4 바이트를 할당 받는다.

0x2000 부터 0x4EDF 까지 할당 받는다. 이때 2,3,4 페이지 가 필요하고 미스가 날때, TLB에 옮겨 놓는다.

0x2000, 0x3000, 0x4000을 엑세스할때는 두번씩, 나머지 주소를 엑세스 할때는 한번씩 총 3003번 물리메모리 엑세스를 한다.

(그림)

TLB도 매우 유용한 이유와 참조의 지역성

TLB를 사용하면, 작은 크기의 TLB도 순차 메모리 액세스 시에 참조의 지역성에 의해 빠른 실행실행 속도를 보인다.

6. 페이징에서 페이지 테이블과 관련된 문제점

1. 1번에 메모리 액세스를 위한 2번의 물리 메모리 액세스

TLB 사용으로 해결한다.

참조의 지역성을 이용해 페이지 테이블의 일부를 CPU패키지 내부 캐시에 가져다 두어 히트시에 1번의 물리 메모리 엑세스가 가능하다.

2. 페이지 테이블의 낭비

프로세스의 실제 크기는 매우 작기 때문에, 대부분의 페이지 테이블 항목이 비어 있는 문제가 있다.

역 페이지 테이블 : 물리 메모리 전체 프레임에 대해, 각 프레임이 어떤 프로세스의 어떤 페이지에 할당되었는지를 나타내는 테이블로 해결한다.

멀티레벨 페이지 : 프로세스가 현재 사용 중인 페이지들에 대해서만 페이지 테이블을 만드는 방식으로 해결한다.